# EC200A Series QuecOpen Reference Design

#### LTE Standard Module Series

Version: 1.2

Date: 2023-08-02

Status: Released

At Quectel, our aim is to provide timely and comprehensive services to our customers. If you require any assistance, please contact our headquarters:

#### Quectel Wireless Solutions Co., Ltd.

Building 5, Shanghai Business Park Phase III (Area B), No.1016 Tianlin Road, Minhang District, Shanghai 200233, China

Tel: +86 21 5108 6236 Email: <u>info@quectel.com</u>

#### Or our local offices. For more information, please visit:

http://www.quectel.com/support/sales.htm.

#### For technical support, or to report documentation errors, please visit:

http://www.quectel.com/support/technical.htm.

Or email us at: support@quectel.com.

### **Legal Notices**

We offer information as a service to you. The provided information is based on your requirements and we make every effort to ensure its quality. You agree that you are responsible for using independent analysis and evaluation in designing intended products, and we provide reference designs for illustrative purposes only. Before using any hardware, software or service guided by this document, please read this notice carefully. Even though we employ commercially reasonable efforts to provide the best possible experience, you hereby acknowledge and agree that this document and related services hereunder are provided to you on an "as available" basis. We may revise or restate this document from time to time at our sole discretion without any prior notice to you.

### **Use and Disclosure Restrictions**

### **License Agreements**

Documents and information provided by us shall be kept confidential, unless specific permission is granted. They shall not be accessed or used for any purpose except as expressly provided herein.

### Copyright

Our and third-party products hereunder may contain copyrighted material. Such copyrighted material shall not be copied, reproduced, distributed, merged, published, translated, or modified without prior written consent. We and the third party have exclusive rights over copyrighted material. No license shall be granted or conveyed under any patents, copyrights, trademarks, or service mark rights. To avoid ambiguities, purchasing in any form cannot be deemed as granting a license other than the normal non-exclusive, royalty-free license to use the material. We reserve the right to take legal action for noncompliance with abovementioned requirements, unauthorized use, or other illegal or malicious use of the material.

#### **Trademarks**

Except as otherwise set forth herein, nothing in this document shall be construed as conferring any rights to use any trademark, trade name or name, abbreviation, or counterfeit product thereof owned by Quectel or any third party in advertising, publicity, or other aspects.

#### **Third-Party Rights**

This document may refer to hardware, software and/or documentation owned by one or more third parties ("third-party materials"). Use of such third-party materials shall be governed by all restrictions and obligations applicable thereto.

We make no warranty or representation, either express or implied, regarding the third-party materials, including but not limited to any implied or statutory, warranties of merchantability or fitness for a particular purpose, quiet enjoyment, system integration, information accuracy, and non-infringement of any third-party intellectual property rights with regard to the licensed technology or use thereof. Nothing herein constitutes a representation or warranty by us to either develop, enhance, modify, distribute, market, sell, offer for sale, or otherwise maintain production of any our products or any other hardware, software, device, tool, information, or product. We moreover disclaim any and all warranties arising from the course of dealing or usage of trade.

### **Privacy Policy**

To implement module functionality, certain device data are uploaded to Quectel's or third-party's servers, including carriers, chipset suppliers or customer-designated servers. Quectel, strictly abiding by the relevant laws and regulations, shall retain, use, disclose or otherwise process relevant data for the purpose of performing the service only or as permitted by applicable laws. Before data interaction with third parties, please be informed of their privacy and data security policy.

### **Disclaimer**

- a) We acknowledge no liability for any injury or damage arising from the reliance upon the information.

- b) We shall bear no liability resulting from any inaccuracies or omissions, or from the use of the information contained herein.

- c) While we have made every effort to ensure that the functions and features under development are free from errors, it is possible that they could contain errors, inaccuracies, and omissions. Unless otherwise provided by valid agreement, we make no warranties of any kind, either implied or express, and exclude all liability for any loss or damage suffered in connection with the use of features and functions under development, to the maximum extent permitted by law, regardless of whether such loss or damage may have been foreseeable.

- d) We are not responsible for the accessibility, safety, accuracy, availability, legality, or completeness of information, advertising, commercial offers, products, services, and materials on third-party websites and third-party resources.

Copyright © Quectel Wireless Solutions Co., Ltd. 2023. All rights reserved.

### **About the Document**

### **Revision History**

| Version | Date       | Author      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------|------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -       | 2022-06-09 | Shiye ZHU   | Creation of the document                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1.0     | 2022-07-26 | Shiye ZHU   | First official release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1.1     | 2023-06-01 | Coco CHEN   | <ol> <li>Changed the required current of the module from 3.0 A to 2.8 A (Sheets 1 &amp; 2 &amp; 5).</li> <li>Added the Notes 5 &amp; 6 (Sheet 3).</li> <li>Added reference design of WLAN interface (Sheets 3, 20, 21 and 22).</li> <li>Changed the wakeup pin of WAKE_UP_MCU from WAKEUP_IN to MAIN_DTR (Sheet 4).</li> <li>Updated the power supply design for SD card, SLIC, WLAN and Ethernet PHYs (Sheet 5).</li> <li>Added two resistors R0807 and R0808 in UART Level-shifting Circuit – IC solution (Sheet 8).</li> <li>Deleted the triode in the STATUS indicator design (Sheet 23).</li> </ol> |

| 1.2     | 2023-08-02 | Julian TANG | <ol> <li>Deleted resistor R1401 on VDD_3V3 trace (Sheet 14).</li> <li>Updated the resistance of R1910 in SLIC design to 3.9 K and added related note (Sheet 19).</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                              |

#### **Contents**

| Ab | out the | e Document   | 3 |

|----|---------|--------------|---|

| Со | ntents  |              | 4 |

| 4  | Defer   | rence Design | 5 |

| 1  | Refer   | rence Design | ວ |

|    | 1.1.    | Introduction | 5 |

|    | 1.2.    | Schematics   | 5 |

## 1 Reference Design

#### 1.1. Introduction

This document provides the reference design for Quectel EC200A series QuecOpen<sup>®</sup> module, including block diagrams of power supply and module design, analog audio, UART, (U)SIM, RGMII/RMII, SD card interfaces, etc.

#### 1.2. Schematics

The schematics illustrated in the following pages are provided for your reference only.

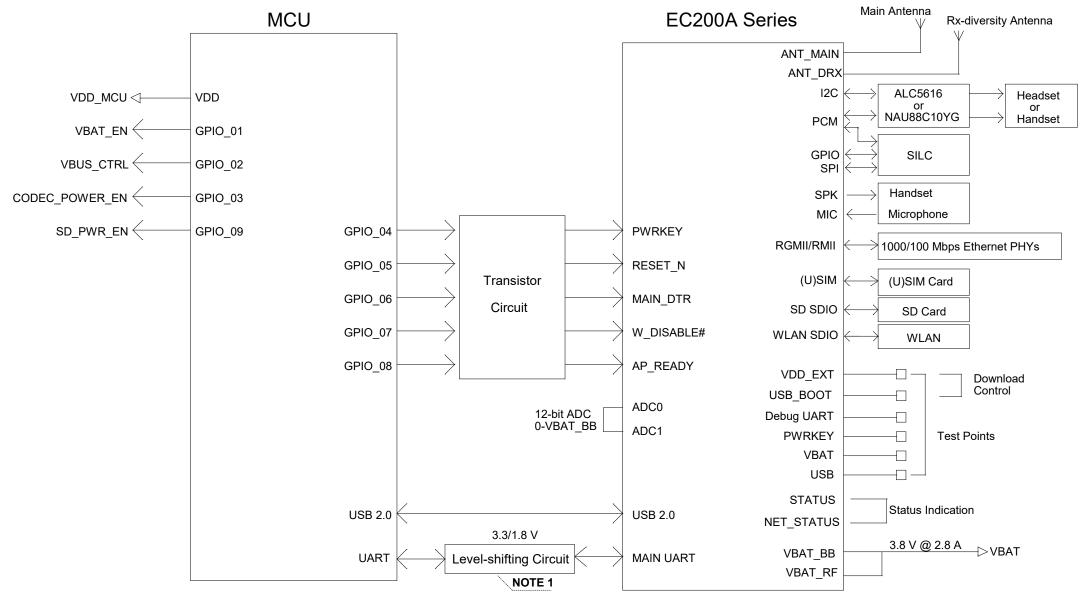

### **Block Diagram**

- 1. A level-shifting circuit or a voltage-level translator TXS0108EPWR provided by Texas Instruments is recommended.

- 2. The power supply should be able to provide sufficient current of at least 2.8 A for the module.

| Quectel Wireless Solutions             |                         |     |            |  |

|----------------------------------------|-------------------------|-----|------------|--|

| PROJECT EC200A Series QuecOpen VER 1.2 |                         |     |            |  |

| DRAWN BY<br>Julian Tang                | CHECKED BY<br>Shiye ZHU |     | SIZE<br>A2 |  |

| DATE Wednesday August (                | 2 2023 SHEET            | - 1 | OF 23      |  |

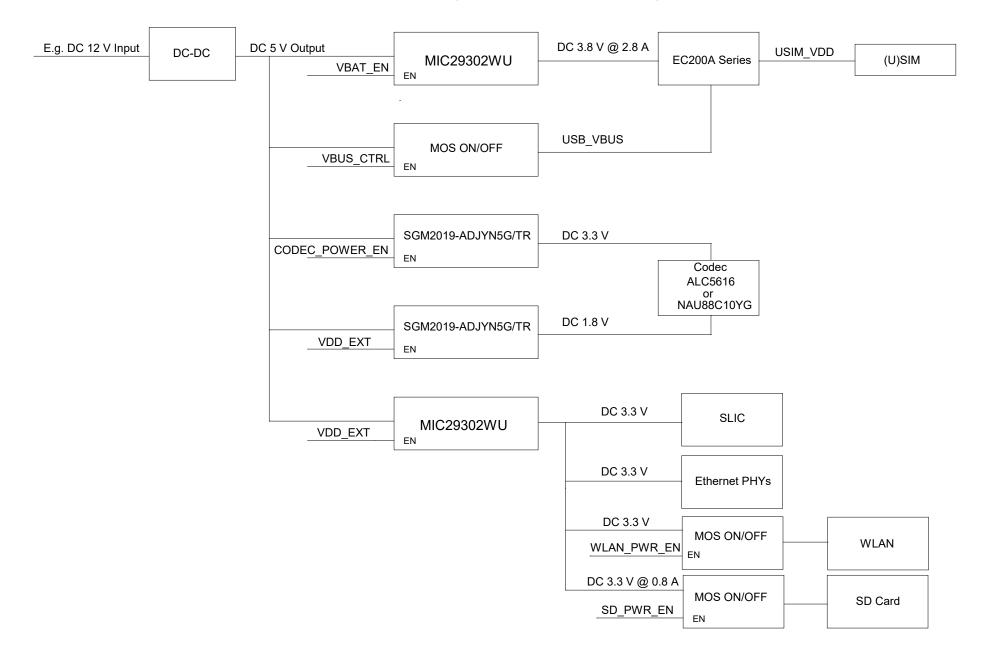

### **Power System Block Diagram**

| Qı       | ıectel Wi        | reless S   | oluti | ions |

|----------|------------------|------------|-------|------|

| PROJECT  | EC200A Series Qu | ecOpen     | VER   | 1.2  |

| DRAWN BY |                  | CHECKED BY |       | SIZE |

|          | Julian Tang      | Shiye ZHU  |       | A2   |

|          |                  |            | _     |      |

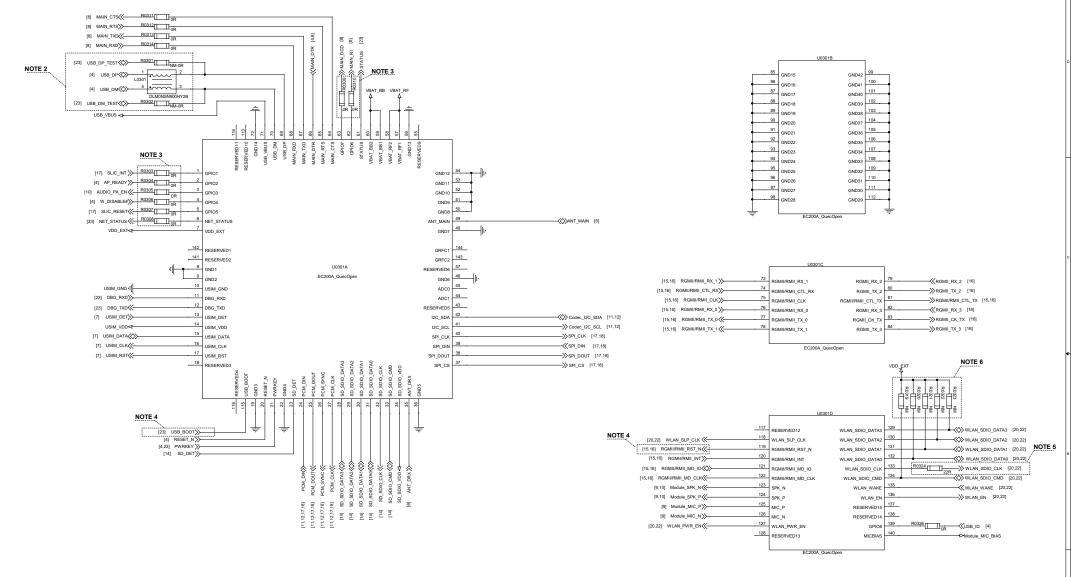

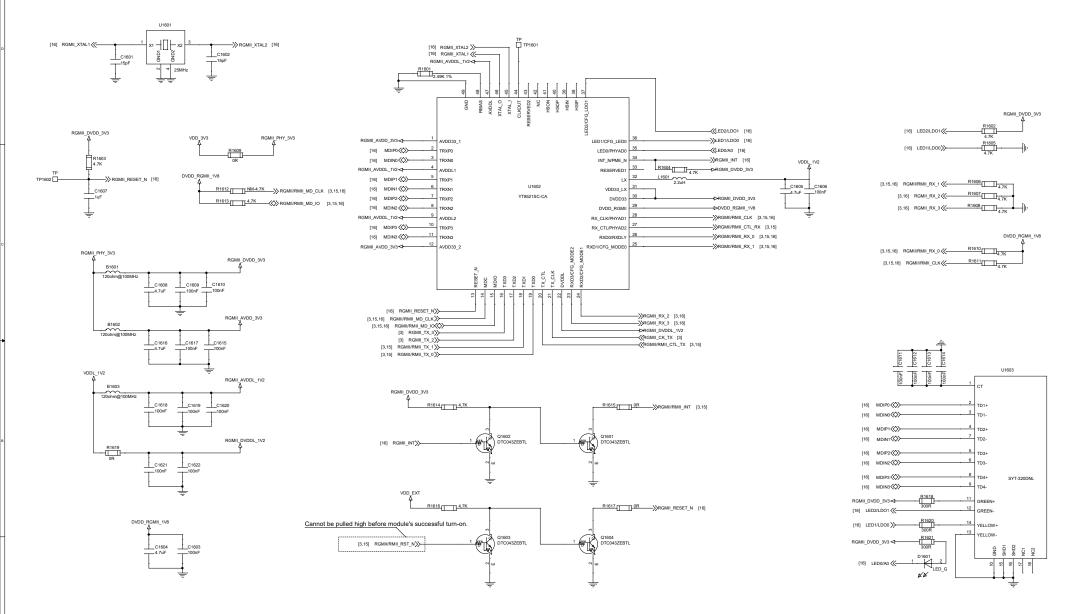

### **Module Interface**

- 1. All GND pins should be connected to the ground, and keep unused and RESERVED pins unconnected. Ensure there is a complete reference ground plane below the module, and the ground plane is as close as possible to the layer where the module is located.

- 2. A common mode choke L0301 is recommended to be added in series between the module and your MCU in order to suppress EMI spurious transmission, and it should be placed close to the module. Meanwhile, it is recommended to reserve the test points for upgrading the firmware over USB interface and minimize the extra stubs of the trace. The R0301 resistors should be placed close to the module to ensure the integrity of USB signal.

- 3. Pins are multiplexed with alternate function, and 0  $\Omega$  resistors are connected in series for the selection of functions in compatible design.

- 4. USB\_BOOT and RGMII/RMII\_RST\_N cannot be pulled up to high level before the module is turned on.

- 5. In order to improve the signal quality, the WLAN\_SDIO\_CLK signal trace needs to be connected with 15–24 Ω resistor in series near the module, and the distance from the WLAN\_SDIO\_CLK pin to the resistor needs to be less than 5 mm.

- 6. To avoid the jitter of bus, pull-up resistors R0319–R0323 are needed to be added to SDIO bus. VDD\_EXT should be used as the pull-up power. The resistance of these resistors are among 10–100 kD and not mounted by default.

| Quectel Wireless Solutions |                     |         |                    |     |            |  |

|----------------------------|---------------------|---------|--------------------|-----|------------|--|

| PROJECT                    | EC200A Series Qui   | ecOpen  |                    | VER | 1.2        |  |

| DRAWN BY                   | Julian Tang         | CHECK   | ŒD BY<br>Shiye ZHU |     | SIZE<br>A2 |  |

| DATE                       | Wednesday, August 0 | 2. 2023 | SHEET              | 3   | OF 23      |  |

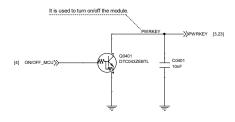

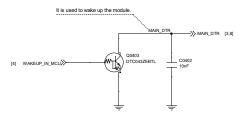

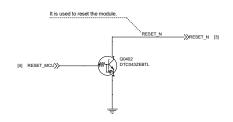

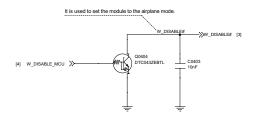

### **MCU Interface**

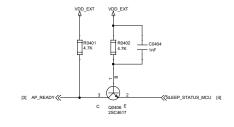

- 1. U0401 represents your MCU. The power domain of GPIO interfaces of the module is 1.8 V. If the GPIO interfaces of U0401 is also 1.8 V, then the related level-shifting circuit is not needed.

- 2. The USB interface of the module serves as a host device or slave device and supports full-speed and high-speed modes of USB 2.0. If you need to use OTG function, it is necessary to distinguish whether the USB is master mode or slave mode by the level change of the USB\_ID pin. The USB\_VBUS pin of the module should be powered by an external power system for USB detection, and VBUS\_CTRL is used to turn onloff the USB\_VBUS power supply.

3. It is recommended to select GPIO pins which are at low level by default as the control pins for PWRKEY and RESET\_N pins does not exceed 10 nF.

Ensure that the load capacitance on PWRKEY and RESET\_N pins does not exceed 10 nF.

| Quectel Wireless Solutions |                         |         |            |  |  |

|----------------------------|-------------------------|---------|------------|--|--|

| PROJECT EC200A Series      | QuecOpen                | VER 1.2 |            |  |  |

| DRAWN BY<br>Julian Tang    | CHECKED BY<br>Shiye ZHL |         | SIZE<br>A2 |  |  |

### **Power Supply Design**

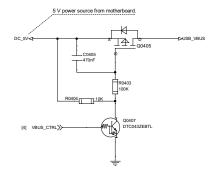

### DC-DC Application

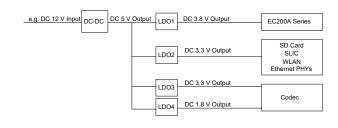

When the input voltage is above 7.0 V, use a DC-DC converter to convert the high input voltage to 5.0 V, and then use LDOs to convert it to 3.8 V, 3.3 V and 1.8 V to power the module, audio PA, Ethernet PHYs, SLIC, WLAN, SD card and Codec.

The supply current of the module must be of at least 2.8 A.

#### **LDO Application**

When the input voltage is below 7.0 V, use an LDO to convert the input voltage to 3.8 V.

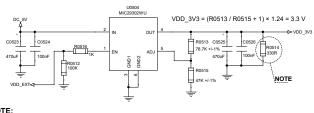

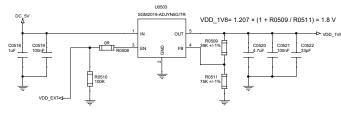

#### Power Supply for SD Card, SLIC, WLAN and Ethernet PHYs

#### NOTE:

The recommended load current is greater than 10 mA.

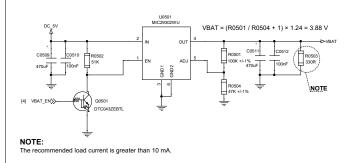

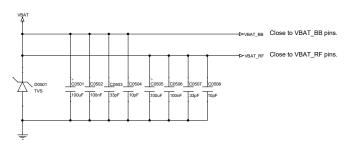

#### **VBAT** Design

#### NOTE:

- 1. The power supply should be able to provide sufficient current of at least 2.8 A for the module.

- 2. VBAT should be routed in star configuration to VBAT\_BB and VBAT\_RF pins.

- 3. The width of VBAT\_BB trace should not be less than 1 mm; and the width of VBAT\_RF trace should not be less than 2 mm.

- 4. The recommended operating voltage of VBAT is 3.4-4.5 V.

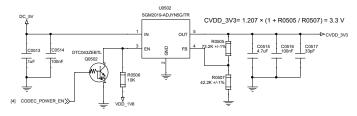

#### **Power Supply for Codec**

#### NOTE:

- 1.VDD\_EXT and CODEC\_POWER\_EN are used to turn on/off VDD\_1V8 and CVDD\_3V3 respectively.

- 2. The following power-up/down sequences should be followed to ensure the audio codec works normally.

Power-up sequence: power up VDD\_1V8 first, and then CVDD\_3V3.

Power-down sequence: power down CVDD\_3V3 first, and then VDD\_1V8.

| Qu       | ectel Wi         | reless S                | oluti | ons        |

|----------|------------------|-------------------------|-------|------------|

| PROJECT  | EC200A Series Qu | VER<br>1.2              |       |            |

| DRAWN BY | Julian Tang      | CHECKED BY<br>Shiye ZHU |       | SIZE<br>A2 |

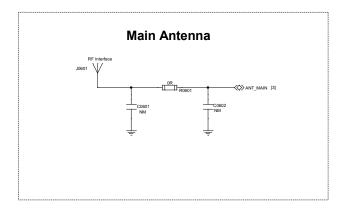

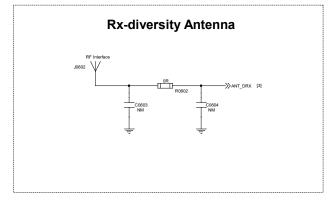

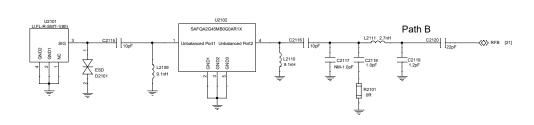

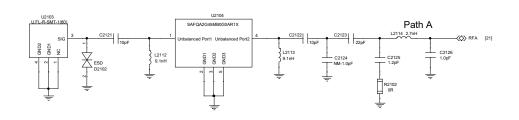

### **Antenna Interface Design**

#### NOTE:

It is highly recommended to reserve a  $\Pi$  type circuit for main and Rx-diversity antennas for future debugging. The impedance of the RF signal traces must be controlled as 50  $\Omega$  when routing.

| Quectel Wireless Solutions |                         |         |            |  |  |

|----------------------------|-------------------------|---------|------------|--|--|

| PROJECT EC200A Series C    | QuecOpen                | VER 1.2 |            |  |  |

| DRAWN BY<br>Julian Tang    | CHECKED BY<br>Shiye ZHU |         | SIZE<br>A2 |  |  |

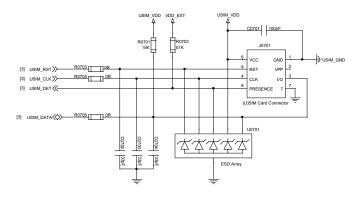

### (U)SIM Interface Design

- 1. U0701 is recommended to be used to offer good ESD protection, and the parasitic capacitance should not be more than 15 pF.

- 2. The pull-up resistor R0701 can improve anti-jamming capability, and should be placed close to the (U)SIM card connector.

- 3. Connect 0 Ω resistors R0703-R0705 in series between the module and (U)SIM card for debugging, and capacitors C0702-C0704 can be used to filter out RF interference.

- 4. C0701's capacitance should be less than 1  $\mu$ F and it should be placed close to the (U)SIM card connector.

- 5. The GND of the (U)SIM card connector is recommended to be connected to the module's USIM\_GND. In addition, USIM\_GND can also be connected to the GND of your PCB directly if the PCB's GND is complete.

- 6. For more information about the layout of (U)SIM interface, please refer to Quectel\_EC200A\_Series\_QuecOpen\_Hardware\_Design.

| Qı       | uectel Wi           | reles  | ss S      | oluti | ions       |  |

|----------|---------------------|--------|-----------|-------|------------|--|

| PROJECT  | EC200A Series Qu    | ecOpen | Open V    |       | /ER<br>1.2 |  |

| DRAWN BY |                     | CHECK  | ŒD BY     | •     | SIZE       |  |

|          | Julian Tang         | *      | Shiye ZHU | 1     | A2         |  |

| DATE     | Wednesday, August 0 | 2 2023 | SHEET     | 7     | OF 23      |  |

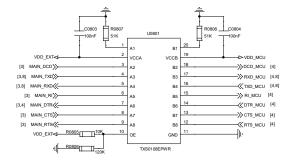

### **UART Interface Design**

#### **UART Level-shifting Circuit - Transistor Solution**

#### **UART Level-shifting Circuit - IC Solution**

- 1. There are two level shifting solutions: transistor solution and IC solution, and the latter one is recommended.

- 2. The power supply of TXS0108EPWR's VCCA should not exceed that of VCCB. For more information, please refer to the datasheet of TXS0108EPWR.

- 3. The transistor solution is not applicable for applications with baud rates exceeding 460 kbps. The capacitors C0801 and C0802 of 1 nF can improve the signal quality.

- MAIN\_RTS and MAIN\_DTR transistor circuits are similar to that of the MAIN\_RXD interface.

MAIN\_CTS, MAIN\_RI and MAIN\_DCD transistor circuits are similar to that of the MAIN\_TXD interface.

| <b>Quectel Wireless Solutions</b> |                   |        |                    |     |            |

|-----------------------------------|-------------------|--------|--------------------|-----|------------|

| PROJECT                           | EC200A Series Qui | ecOpen |                    | VER | 1.2        |

| DRAWN BY                          | Julian Tang       | CHECK  | ED BY<br>Shiye ZHU |     | SIZE<br>A2 |

| DATE We                           | dnesday August 0  | 2 2023 | SHFFT              | 8   | OF 23      |

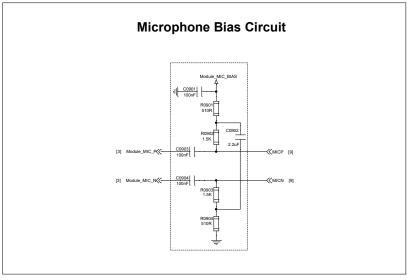

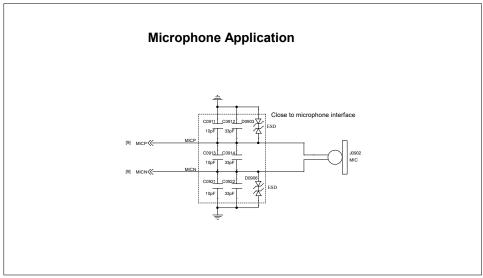

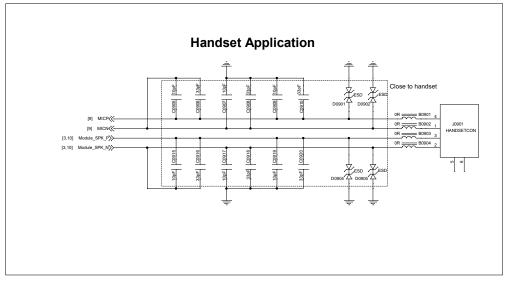

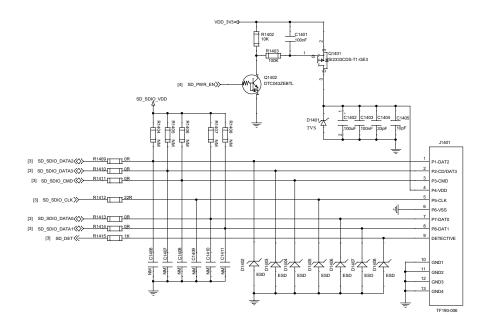

### **Analog Audio Design**

- 1. Both the MIC and SPK signal traces need to be routed as differential pairs.

- 2. All MIC and SPK signal traces should be surrounded with ground on the layer and ground planes above and below, and far away from interferences.

- 3. In the audio design, your can choose either the analog audio or the codec.

- 4. 10 pF and 33 pF capacitors are used to filter TDD noises.

- 5. The analog output only drives handset. For larger power loads such as loudspeaker, an audio power amplifier should be added in the design.

|          | ectel Wi           | reles   | s S                | oluti | ons        |

|----------|--------------------|---------|--------------------|-------|------------|

| PROJECT  | EC200A Series Qu   | ecOpen  |                    | VER   | 1.2        |

| DRAWN BY | Julian Tang        | CHECK   | ED BY<br>Shiye ZHU |       | SIZE<br>A2 |

| DATE W   | ednesday, August 0 | 2. 2023 | SHEET              | 9     | OF 23      |

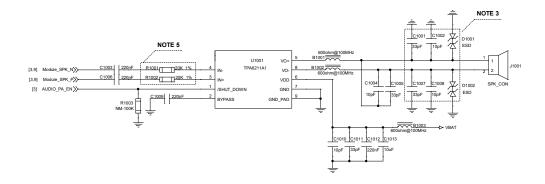

### **Analog Audio Design (Audio Power Amplifier)**

- 1. SPK\_P and SPK\_N are differential output channels that can be used for external audio power amplifier.

- It is recommended to select one pin of the module to control the enable pin of the audio power amplifier to eliminate Pop noise. For more information about AUDIO\_PA\_EN, please contact Quectel Technical Support.

- 2. The amplifier model in this design is for reference only. Select the audio power amplifier with appropriate power according to actual needs.

- 3. Place filter capacitors and ESD protection components close to the loudspeaker.

- 4. The selection of ESD device is related to the selection of audio power amplifier. Ensure that the output audio voltage of audio power amplifier is within the maximum reverse working voltage range of ESD device under normal working condition to avoid damage to ESD device.

- 5. R1001 and R1002 can adjust the gain of the power amplifier, please refer to the datasheet of TPA6211A1 for details.

| Quectel Wi               | reless S                | oluti   | ons        |

|--------------------------|-------------------------|---------|------------|

| PROJECT EC200A Series Qu | ecOpen                  | VER 1.2 |            |

| DRAWN BY<br>Julian Tang  | CHECKED BY<br>Shiye ZHU |         | SIZE<br>A2 |

| DATE Wednesday, August 0 | 12. 2023   SHEET        | 10      | OF 23      |

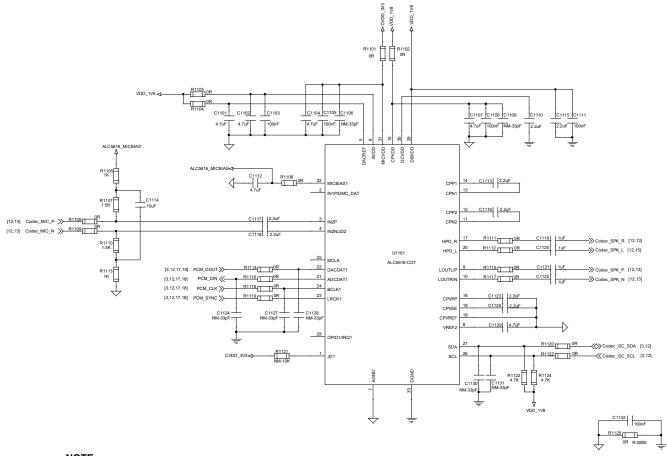

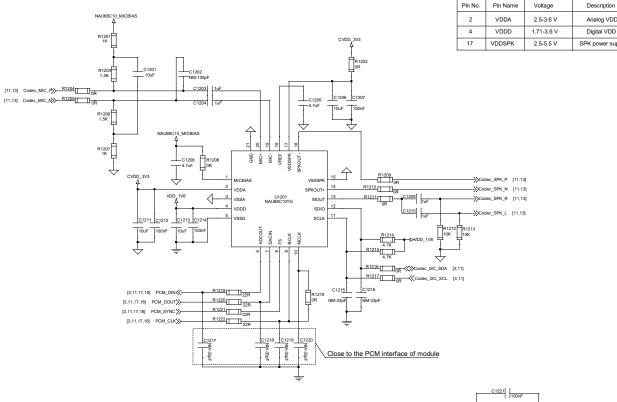

### **Audio Codec Design (ALC5616)**

- $1. \ ALC5616 \ power-up \ sequence: DBVDD/I2C \ pull-up \ power/AVDD/DACREF/CPVDD \rightarrow MICVDD \rightarrow software \ initialization.$

- 2. ALC5616 power-down sequence: disable codec function by software  $\rightarrow$  MICVDD  $\rightarrow$  DBVDD/I2C pull-up power/AVDD/DACREF/CPVDD.

- 3. The module will automatically initialize the codec via I2C interface after it is turned on successfully, so all power supplies for the codec need to be powered on before that.

- 4. Pay attention to the distinction between analog ground and digital ground. The analog ground and digital ground need to be connected with a 0 Ω resistor packaged as R-0805. For more details, please refer to Sheet "Audio Codec Interface Design".

- 5. For more details, please refer to the datasheet of ALC5616.

| Quectel Wireless Solutions |                         |         |            |  |

|----------------------------|-------------------------|---------|------------|--|

| PROJECT EC200A Series Qu   | ecOpen                  | VER 1.2 |            |  |

| DRAWN BY<br>Julian Tang    | CHECKED BY<br>Shiye ZHU |         | SIZE<br>A2 |  |

### Audio Codec Design (NAU88C10YG)

- The codec should be away from interference sources such as RF and power supplies, and the codec audio signal should be surrounded with ground as much as possible.

- 2. The voltage of VDDA pin must always be greater than that of VDDD.

- The analog ground and digital ground need to be connected with a 0 Ω resistor packaged as R-0805. For more details, please refer to sheet "Audio Codec Interface Design".

- 4. For more details, please refer to the datasheet of NAU88C10YG.

| 2  | VDDA   | 2.5-3.6 V  | Analog VDD       |

|----|--------|------------|------------------|

| 4  | VDDD   | 1.71-3.6 V | Digital VDD      |

| 17 | VDDSPK | 2.5-5.5 V  | SPK power supply |

|    | •      | •          |                  |

| <b>Quectel Wireless Solutions</b> |                        |            |     |      |

|-----------------------------------|------------------------|------------|-----|------|

| PROJECT                           | EC200A Series QuecOpen |            | VER | 1.2  |

| DRAWN BY                          |                        | CHECKED BY |     | SIZE |

|                                   | Julian Tang            | Shiye ZHU  |     | A2   |

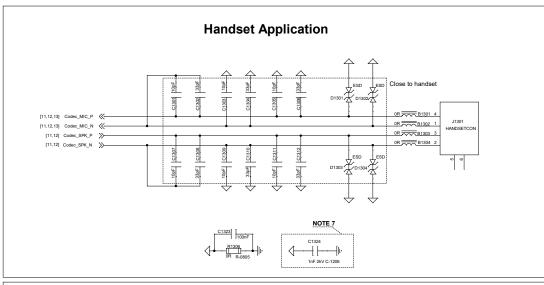

### **Audio Codec Interface Design**

- 1. The codec analog output can drive handset and headset. For larger power loads such as loudspeaker, an audio power amplifier should be added in the design.

- 2. In handset applications, both the MIC and SPK signal traces need to be routed as differential pairs.

- In headset applications, route the MIC signal traces as a differential pair.

- 4. All MIC and SPK signal traces should be surrounded with ground on the layer and ground planes above and below, and far away from noises such as clock and DC-DC signals.

- 5. Pay attention to the distinction between analog ground and digital ground. The analog ground and digital ground need to be connected with a 0 Ω resistor packaged as R-0805 (a via directly to main GND).

- 6. You can choose either ALC5616 or NAG88C10YG in audio codec design.

- 7. C1324 and C1325 capacitors are used for electrostatic protection, and they need to be placed close to D1301, D1302, D1303, D1304 and D1305, D1306, D1307 respectively, and connected to the main ground nearby.

| Quectel Wi                     | ons                     |         |            |

|--------------------------------|-------------------------|---------|------------|

| PROJECT EC200A Series QuecOpen |                         | VER 1.2 |            |

| DRAWN BY<br>Julian Tang        | CHECKED BY<br>Shiye ZHU |         | SIZE<br>A2 |

| DATE Wednesday August 0        | 2 2023 SHEET            | 13      | OF 23      |

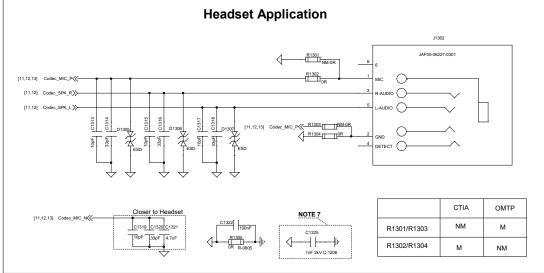

### **SD Card Interface Design**

- 1. The SD\_SDIO\_VDD can only be used for the pull-up resistor of SDIO bus and its maximum output current is 50 mA.

- 2. The voltage range of SD card power supply VDD is 2.7–3.6 V and a sufficient current of at least 0.8 A should be provided.

- 3. To avoid the jitter of bus, pull-up resistors R1404–R1408 are needed to be added to SDIO bus, SD\_SDIO\_VDD should be used as the pull-up power. The resistance of these resistors are among 10–100 k $\Omega$  and the recommended value is 100 k $\Omega$ .

- 4. To adjust the signal quality, it is recommended to add resistors R1409–R1414 in series between the module and the SD card connector. The recommended resistance of R1412 is 22 Ω and the others is 0 Ω. The bypass capacitors C1406–C1411 are reserved and not mounted by default.

- 5. To offer good ESD protection, it is recommended to add ESD protective device on SD card pins near the SD card connector with junction capacitance less than 8 pF.

- 6. Keep SDIO signals far away from other sensitive circuits/signals such as RF circuits, analog signals, as well as noisy signals such as clock and DC-DC signals.

- 7. It is important to route the SDIO signal traces with ground surrounded. The impedance of SDIO data trace is 50  $\Omega$  (±10 %).

- 8. It is recommended to keep the traces of SD\_SDIO\_CLK, SD\_SDIO\_DATA[0:3] and SD\_SDIO\_CMD with equal length (the difference among them is less than 1 mm) and the total routing length needs to be less than 50 mm.

- 9. Make sure the adjacent trace spacing is twice the trace width and the bus capacitance is less than 15 pF

| Qu       | ectel Wi               | reless    | Soluti | ions |

|----------|------------------------|-----------|--------|------|

| PROJECT  | EC200A Series QuecOpen |           | VER    | 1.2  |

| DRAWN BY |                        | CHECKED B | γ '    | SIZE |

|          | Julian Tang            | Shiye 2   | ZHU    | A2   |

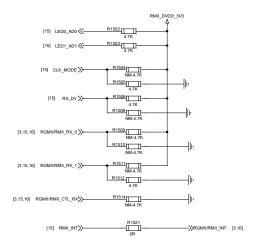

### **RMII Design (100 Mbps Ethernet)**

- 1. Keep data signal traces and control signal traces of RMII interfaces far away from sensitive circuits and signals such as RF signals, analog signals, and noise signals generated by clock, DC-DC.

- 2. The single-ended impedance of RMII data trace is 50  $\Omega$  ±10 %.

- 3. The length difference of RGMII/RMII\_TX\_[0:1] and RGMII/RMII\_CTL\_TX should be less than 2 mm, and the spacing between the signal traces should be larger than twice the trace width. Similarly, the length difference of RGMII/RMII\_RX\_[0:1], RGMII/RMII\_CTL\_RX and RGMII/RMII\_CLK should be less than 2 mm, and the spacing between the signal traces should be larger than twice the trace width.

- 4. Spacing between Tx bus and Rx bus is larger than 2.5 times of the trace width.

- 5. Spacing between Tx/Rx bus and other signals is larger than 3 times of the trace width.

- 6. It is recommended to use a level-shifting chip without pull-up for the level-shifting circuit.

- 7. For more details, please refer to the datasheet of YT8512H.

| Quectel Wireless Solutions |                         |         |  |

|----------------------------|-------------------------|---------|--|

| PROJECT EC200A Se          | ries QuecOpen           | VER 1.2 |  |

| DRAWN BY<br>Julian Tang    | CHECKED BY<br>Shiye ZHL | J SIZE  |  |

| DATE Wednesday A           | Junust 02 2023   SHFFT  | 150F 23 |  |

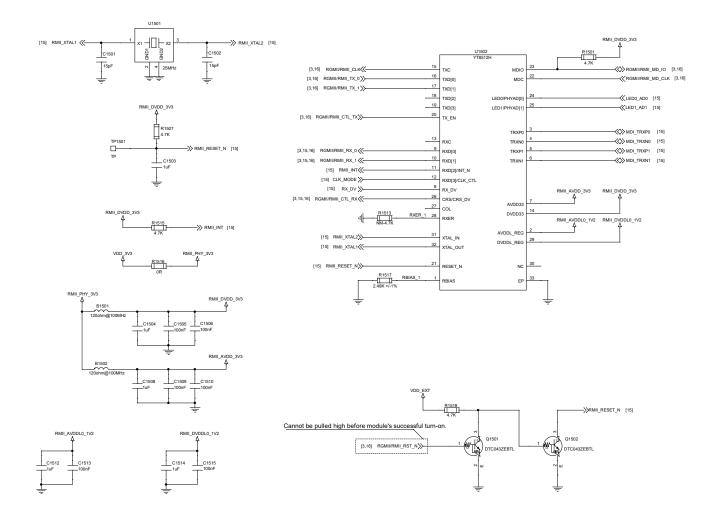

### **RGMII** Design (1000 Mbps Ethernet)

#### NOTE

- 1. Keep data signal traces and control signal traces of RGMII interfaces far away from sensitive circuits and signals like RF signals, analog signals, and noise signals generated by clock, DC-DC, etc.

- 2. The single-ended impedance of RGMII data trace is 50  $\Omega$  ±10 %.

- 3. The length difference of RGMII/RMII\_TX\_[0:1], RGMII\_TX\_[2:3], RGMII/RMII\_CTL\_TX and RGMII\_CK\_TX should be less than 0.25 mm, and the spacing between the signal traces should be larger than twice the trace width. Similarly, the length difference of RGMII/RMII\_RX\_[0:1], RGMII\_RX\_[2:3], RGMII/RMII\_CLK\_X and RGMII/RMII\_CLK should be less than 0.25 mm, and the spacing between the signal traces should be larger than twice

- Spacing between Tx bus and Rx bus is larger than 2.5 times of the trace width.

- Spacing between Tx/Rx bus and other signals is larger than 3 times of the trace width.

- 6. It is recommended to use a level shifting chip without pull-up for the level-shifting circuit.

- For more details, please refer to the datasheet of YT8521SC.

| Quectel Wireless Solutions     |                     |         |                    |    | ons        |

|--------------------------------|---------------------|---------|--------------------|----|------------|

| PROJECT EC200A Series QuecOpen |                     |         | VER 1.2            |    |            |

| DRAWN BY                       | Julian Tang         | CHECK   | ED BY<br>Shiye ZHU |    | SIZE<br>A2 |

| DATE                           | Wednesday, August 0 | 2. 2023 | SHEET              | 16 | OF 23      |

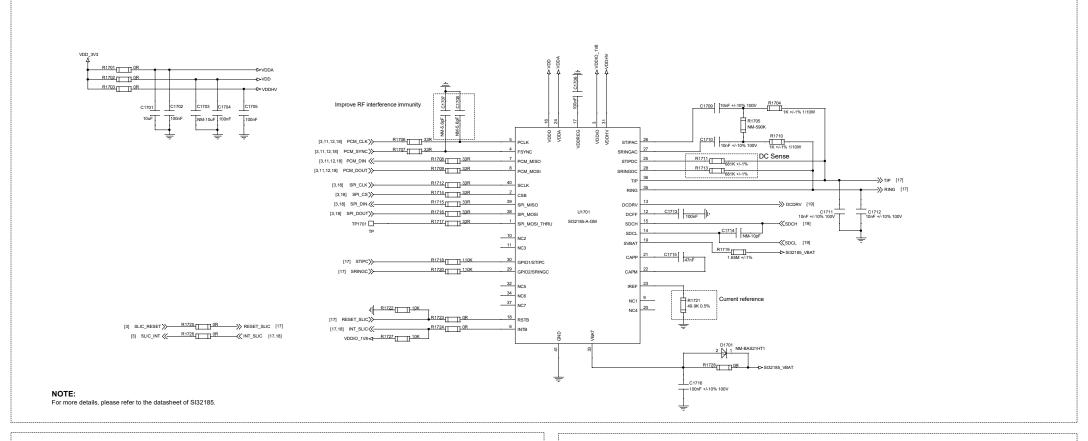

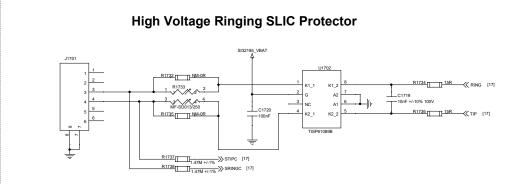

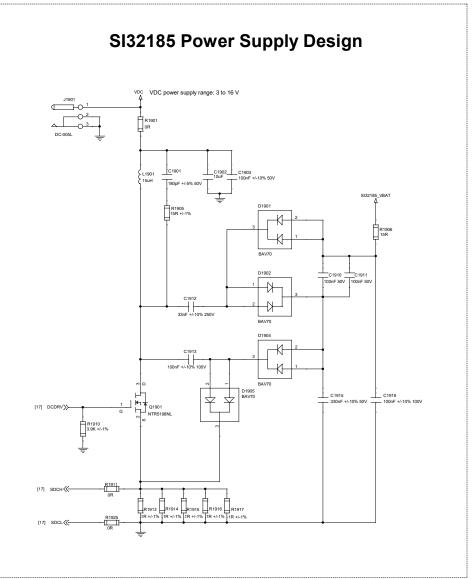

### SLIC Design (SI32185)

|                          | uectel Wi          | reles            | ss S               | oluti | ions       |  |

|--------------------------|--------------------|------------------|--------------------|-------|------------|--|

| PROJECT EC200A Series Qu |                    | QuecOpen VER 1.2 |                    | 1.2   |            |  |

| DRAWN BY                 | Julian Tang        | CHECK            | ŒD BY<br>Shiye ZHU |       | SIZE<br>A2 |  |

| DATE                     | Wednesday August 0 | 2 2023           | SHEET              | 17    | OF 23      |  |

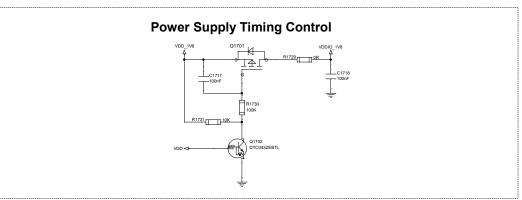

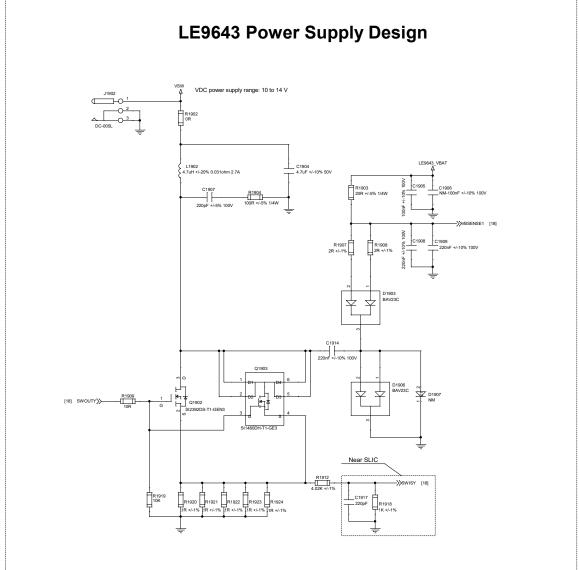

### SLIC Design (LE9643)

#### NOTE

- 1. If you need SLIC interrupt function, you need to connect INT\_SLIC to pin 1 of the module, and modify the GPIO configuration of pin 1 of the module through software.

- 2. For more details, please refer to the datasheet of LE9643.

| Quectel Wi               | reless S                | oluti   | ons        |

|--------------------------|-------------------------|---------|------------|

| PROJECT EC200A Series Qu |                         | VER 1.2 |            |

| DRAWN BY<br>Julian Tang  | CHECKED BY<br>Shiye ZHU | i       | SIZE<br>A2 |

| DATE Wednesday, August 0 | 2. 2023 SHEET           | 18      | OF 23      |

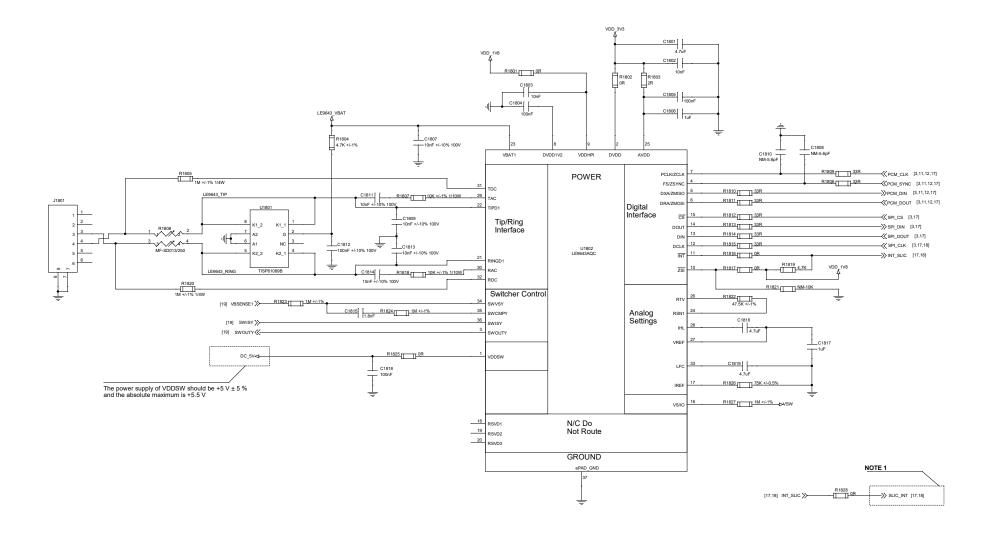

### **SLIC Power Supply Design**

#### NOTE:

R1910 must be reserrved to protect Q1901 from damage

| Quectel Wireless Solutions     |                       |       |            |  |  |

|--------------------------------|-----------------------|-------|------------|--|--|

| PROJECT EC200A Series QuecOpen |                       | VER   | VER 1.2    |  |  |

| DRAWN BY<br>Julian Tang        | CHECKED BY<br>Shiye Z |       | SIZE<br>A2 |  |  |

| DATE Wednesday Augus           | 1 02 2023 SHF         | FT 19 | OF 23      |  |  |

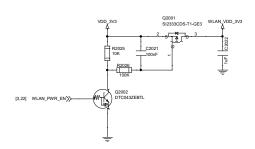

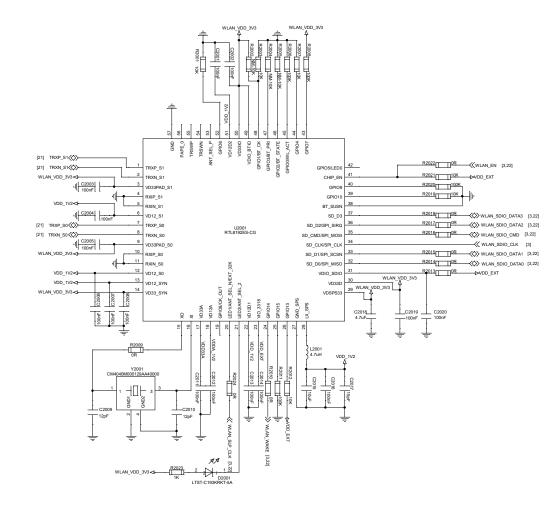

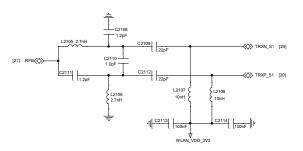

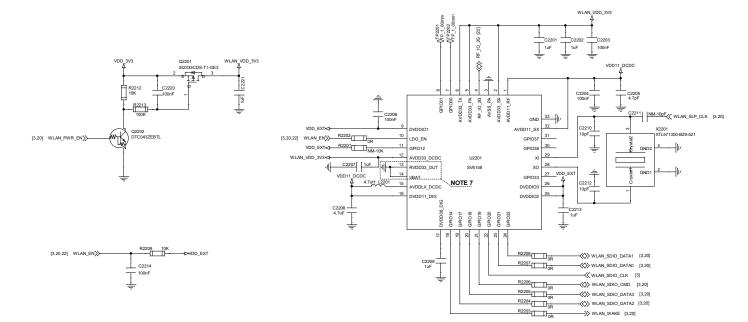

### WLAN Design (RTL8192)

- 1. In order to adjust the signal quality, it is recommended to add 0 Ω resistors R2014–R2018 in series between the module and the RTL8192.

- 2. Keep SDIO signals far away from other sensitive circuits/signals such as RF circuits, analog signals, as well as noisy signals such as clock and DC-DC signals.

- 3. It is important to route the SDIO signal traces with ground surrounded. The impedance of SDIO data trace is 50  $\Omega$  (±10 %).

- 4. It is recommended to keep the traces of WLAN\_SDIO\_CLK, WLAN\_SDIO\_DATA(0:3) and WLAN\_SDIO\_CMD with equal length (the difference among them is less than 1 mm) and the total routing length needs to be less than 50 mm.

- 5. Make sure the adjacent trace spacing is twice the trace width and the bus capacitance is less than 15 pF.

| Quectel V               | Vireless S              | oluti | ions       |

|-------------------------|-------------------------|-------|------------|

| PROJECT EC200A Series   | EC200A Series QuecOpen  |       | 1.2        |

| DRAWN BY<br>Julian Tang | CHECKED BY<br>Shiye ZHU |       | SIZE<br>A2 |

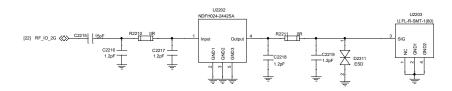

### RTL8192 RF Design

#### NOTE:

The impedance of the RF signal traces must be controlled as 50  $\ensuremath{\Omega}$  when routing.

| Quectel Wireless Solutions     |                    |         |                    |    |            |   |

|--------------------------------|--------------------|---------|--------------------|----|------------|---|

| PROJECT EC200A Series QuecOpen |                    | VER 1.2 |                    |    |            |   |

| DRAWN BY                       | Julian Tang        | CHECK   | ED BY<br>Shiye ZHU |    | SIZE<br>A2 |   |

| DATE                           | Wednesday August 0 | 2 2023  | SHEET              | 21 | OF 23      | _ |

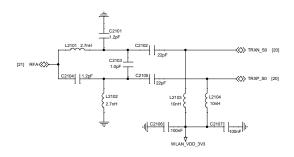

### WLAN Design (SV6158)

#### NOTE

- 1. In order to adjust the signal quality, it is recommended to add 0 Ω resistors R2203–R2208 in series between the module and the SV6158.

- 2. Keep SDIO signals far away from other sensitive circuits/signals such as RF circuits, analog signals, as well as noisy signals such as clock and DC-DC signals.

- 3. It is important to route the SDIO signal traces with ground surrounded. The impedance of SDIO data trace is 50 Ω (±10 %).

- 4. It is recommended to keep the traces of WLAN\_SDIO\_CLK, WLAN\_SDIO\_DATA[0:3] and WLAN\_SDIO\_CMD with equal length (the difference among them is less than 1 mm) and the total routing length needs to be less than 50 mm.

- 5. Make sure the adjacent trace spacing is twice the trace width and the bus capacitance is less than 15 pF.

- 6. The impedance of the RF signal traces must be controlled as 50  $\Omega$  when routing.

- 7. In 5 V application, VBAT connects to 5 V, and RVDD33 can provide 3.3 V. In 3.3 V application, VBAT connects to 0 V, and RVDD33 is connected to 0 V as well.

| Quectel Wireless Solutions |                         |  |            |  |  |  |  |

|----------------------------|-------------------------|--|------------|--|--|--|--|

| PROJECT EC200A Series C    | EC200A Series QuecOpen  |  | VER 1.2    |  |  |  |  |

| DRAWN BY<br>Julian Tang    | CHECKED BY<br>Shiye ZHU |  | SIZE<br>A2 |  |  |  |  |

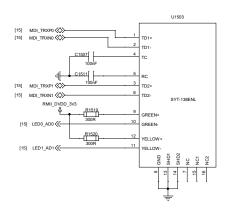

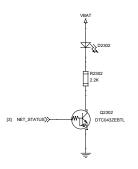

### **Other Designs**

#### **Indicators**

- The STATUS is an open drain output pin.

- 2. For more details about STATUS and NET\_STATUS, please refer to <code>Quectel\_EC200A\_Series\_QuecOpen\_Hardware\_Design</code>.

- 3. If the low current consumption is required when your device is in sleep mode, replace the power supply VBAT of the STATUS and NET\_STATUS indicators with external controllable ones, which can be turned off when the module is in sleep mode to reduce the power consumption.

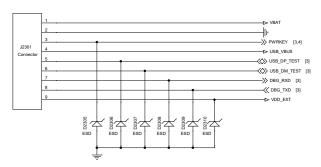

#### **Reserved Test Points**

- 1. Test points for both USB and debug UART interfaces are reserved for capturing logs.

- 2. Test points for USB interface can also be reserved for firmware upgrade.

- 3. The junction capacitance of the ESD protection components on USB data traces should be less than 2 pF.

- The debug UART interface supports 1.8 V power domain, and a voltage-level translator should be used

if the power domain of your application is 3.3 V.

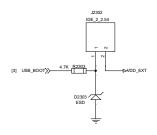

#### **USB\_BOOT Interface**

- 1. It is recommended to reserve the USB\_BOOT interface design.

- USB\_BOOT is kept open by default.

Pull up USB\_BOOT to VDD\_EXT to make the module enter emergency download mode before it is turned on.

In this mode, the module supports firmware upgrade over USB interface.

| Quectel Wireless Solutions |                        |        |           |  |       |

|----------------------------|------------------------|--------|-----------|--|-------|

| PROJECT                    | EC200A Series QuecOpen |        | VER 1.2   |  |       |

| DRAWN BY                   |                        | CHECH  | ŒD BY     |  | SIZE  |

|                            | Julian Tang            |        | Shiye ZHU |  | A:    |

| DATE                       | M-dd A                 | 0 0000 | CUEET     |  | OF 00 |